ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତର ହେଉଛି ଏକ ନିର୍ଦ୍ଦିଷ୍ଟ ଏକକ ସ୍ଫଟିକ୍ ଚଳଚ୍ଚିତ୍ର ଯାହାକି ଇଫେକ୍ସିଆଲ୍ ପ୍ରକ୍ରିୟା ଦ୍ୱାରା ୱେଫର୍ରେ ବ grown ିଥାଏ ଏବଂ ସବଷ୍ଟ୍ରେଟ୍ ୱେଫର୍ ଏବଂ ଏପିଟାକ୍ସିଆଲ୍ ଫିଲ୍ମକୁ ଏପିଟାକ୍ସିଆଲ୍ ୱେଫର୍ କୁହାଯାଏ | କଣ୍ଡକ୍ଟିଭ୍ ସିଲିକନ୍ କାର୍ବାଇଡ୍ ସବଷ୍ଟ୍ରେଟ୍ ଉପରେ ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତର ବ By ାଇ, ସିଲିକନ୍ କାର୍ବାଇଡ୍ ସମଲିଙ୍ଗୀ ଏପିଟାକ୍ସିଆଲ୍ ୱେଫର୍ ସ୍କଟ୍କି ଡାୟୋଡ୍, MOSFETs, IGBT ଏବଂ ଅନ୍ୟାନ୍ୟ ଶକ୍ତି ଉପକରଣରେ ଅଧିକ ପ୍ରସ୍ତୁତ ହୋଇପାରିବ, ଯେଉଁଥିରେ 4H-SiC ସବଷ୍ଟ୍ରେଟ୍ ସର୍ବାଧିକ ବ୍ୟବହୃତ ହୁଏ |

ସିଲିକନ୍ କାର୍ବାଇଡ୍ ପାୱାର୍ ଡିଭାଇସ୍ ଏବଂ ପାରମ୍ପାରିକ ସିଲିକନ୍ ପାୱାର୍ ଡିଭାଇସ୍ ର ବିଭିନ୍ନ ଉତ୍ପାଦନ ପ୍ରକ୍ରିୟା ହେତୁ ଏହା ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏକକ ସ୍ଫଟିକ୍ ସାମଗ୍ରୀ ଉପରେ ସିଧାସଳଖ ତିଆରି ହୋଇପାରିବ ନାହିଁ | ଅତିରିକ୍ତ ଉଚ୍ଚ-ଗୁଣାତ୍ମକ ଏପିଟାକ୍ସିଆଲ୍ ସାମଗ୍ରୀଗୁଡିକ କଣ୍ଡକ୍ଟିଭ୍ ସିଙ୍ଗଲ୍ ସ୍ଫଟିକ୍ ସବଷ୍ଟ୍ରେଟ୍ ଉପରେ ବ must ଼ିବା ଆବଶ୍ୟକ ଏବଂ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରରେ ବିଭିନ୍ନ ଉପକରଣ ପ୍ରସ୍ତୁତ କରାଯିବା ଆବଶ୍ୟକ | ତେଣୁ, ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଗୁଣ ଉପକରଣର କାର୍ଯ୍ୟଦକ୍ଷତା ଉପରେ ବହୁତ ପ୍ରଭାବ ପକାଇଥାଏ | ବିଭିନ୍ନ ଶକ୍ତି ଉପକରଣଗୁଡ଼ିକର କାର୍ଯ୍ୟଦକ୍ଷତାର ଉନ୍ନତି ମଧ୍ୟ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଘନତା, ଡୋପିଂ ଏକାଗ୍ରତା ଏବଂ ତ୍ରୁଟି ପାଇଁ ଅଧିକ ଆବଶ୍ୟକତା ରଖେ |

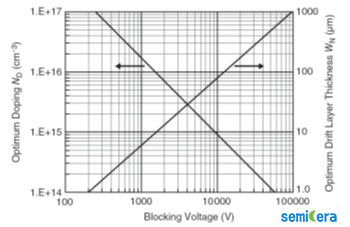

ସଂଖ୍ୟା କିମ୍ବା ପ୍ରତୀକ ସହିତ ଅକ୍ଷର ମଧ୍ଯ ବ୍ୟବହାର କରି। ଡୋପିଂ ଏକାଗ୍ରତା ଏବଂ ୟୁନିପୋଲାର୍ ଡିଭାଇସର ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଘନତା ଏବଂ ଭୋଲଟେଜ୍ ଅବରୋଧ ମଧ୍ୟରେ ସମ୍ପର୍କ |

SIC epitaxial ସ୍ତରର ପ୍ରସ୍ତୁତି ପ୍ରଣାଳୀରେ ମୁଖ୍ୟତ ev ବାଷ୍ପୀକରଣ ଅଭିବୃଦ୍ଧି ପଦ୍ଧତି, ତରଳ ପର୍ଯ୍ୟାୟ ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧି (LPE), ମଲିକୁଲାର ବିମ୍ ଏପିଟାକ୍ସିଆଲ୍ ବୃଦ୍ଧି (MBE) ଏବଂ ରାସାୟନିକ ବାଷ୍ପ ଜମା (CVD) ଅନ୍ତର୍ଭୁକ୍ତ | ବର୍ତ୍ତମାନ, କାରଖାନାଗୁଡ଼ିକରେ ବୃହତ ଉତ୍ପାଦନ ପାଇଁ ବ୍ୟବହୃତ ରାସାୟନିକ ବାଷ୍ପ ଜମା (CVD) ହେଉଛି ମୁଖ୍ୟ ପଦ୍ଧତି |

| ପ୍ରସ୍ତୁତି ପଦ୍ଧତି | | ପ୍ରକ୍ରିୟାର ଲାଭ | ପ୍ରକ୍ରିୟାର ଅସୁବିଧା | |

|

ତରଳ ପର୍ଯ୍ୟାୟ ଏପିଟାକ୍ସିଆଲ୍ ବୃଦ୍ଧି |

(LPE)

|

ସରଳ ଯନ୍ତ୍ରପାତି ଆବଶ୍ୟକତା ଏବଂ ସ୍ୱଳ୍ପ ମୂଲ୍ୟର ଅଭିବୃଦ୍ଧି ପଦ୍ଧତି | |

ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଭୂପୃଷ୍ଠ ମର୍ଫୋଲୋଜି ନିୟନ୍ତ୍ରଣ କରିବା କଷ୍ଟକର | ଯନ୍ତ୍ରପାତି ଏକାସାଙ୍ଗରେ ଏକାଧିକ ୱାଫର୍ ଏପିଟାକ୍ସିଆଲ୍ କରିପାରିବ ନାହିଁ, ବହୁ ଉତ୍ପାଦନକୁ ସୀମିତ କରେ | |

|

ମଲିକୁଲାର ବିମ୍ ଏପିଟାକ୍ସିଆଲ୍ ଅଭିବୃଦ୍ଧି (MBE)

|

ନିମ୍ନ ଅଭିବୃଦ୍ଧି ତାପମାତ୍ରାରେ ବିଭିନ୍ନ ସିସି ସ୍ଫଟିକ୍ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରଗୁଡିକ ବୃଦ୍ଧି କରାଯାଇପାରେ | |

ଯନ୍ତ୍ରପାତି ଭାକ୍ୟୁମ୍ ଆବଶ୍ୟକତା ଅଧିକ ଏବଂ ବ୍ୟୟବହୁଳ ଅଟେ | ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଧୀର ଅଭିବୃଦ୍ଧି ହାର | |

|

ରାସାୟନିକ ବାଷ୍ପ ଜମା (CVD) |

କାରଖାନାଗୁଡ଼ିକରେ ବହୁ ଉତ୍ପାଦନ ପାଇଁ ସବୁଠାରୁ ଗୁରୁତ୍ୱପୂର୍ଣ୍ଣ ପଦ୍ଧତି | ମୋଟା ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତର ବ growing ିବାବେଳେ ଅଭିବୃଦ୍ଧି ହାରକୁ ସଠିକ୍ ଭାବରେ ନିୟନ୍ତ୍ରଣ କରାଯାଇପାରିବ | |

SiC epitaxial ସ୍ତରଗୁଡ଼ିକରେ ତଥାପି ବିଭିନ୍ନ ତ୍ରୁଟି ରହିଥାଏ ଯାହା ଉପକରଣର ବ characteristics ଶିଷ୍ଟ୍ୟକୁ ପ୍ରଭାବିତ କରିଥାଏ, ତେଣୁ SiC ପାଇଁ epitaxial ଅଭିବୃଦ୍ଧି ପ୍ରକ୍ରିୟାକୁ କ୍ରମାଗତ ଭାବରେ ଅପ୍ଟିମାଇଜ୍ କରାଯିବା ଆବଶ୍ୟକ | (TaCଆବଶ୍ୟକ, ସେମିକେରା ଦେଖନ୍ତୁ |TaC ଉତ୍ପାଦ |) |

|

ବାଷ୍ପ ବୃଦ୍ଧି ପଦ୍ଧତି |

|

ସିସି ସ୍ଫଟିକ୍ ଟାଣିବା ପରି ସମାନ ଉପକରଣ ବ୍ୟବହାର କରି, ପ୍ରକ୍ରିୟା ସ୍ଫଟିକ୍ ଟାଣିବା ଠାରୁ ସାମାନ୍ୟ ଭିନ୍ନ | ପରିପକ୍ୱ ଉପକରଣ, କମ୍ ମୂଲ୍ୟ | |

SiC ର ଅସମାନ ବାଷ୍ପୀକରଣ ଏହାର ବାଷ୍ପୀକରଣକୁ ଉଚ୍ଚ ଗୁଣବତ୍ତା ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତର ବ grow ାଇବା ପାଇଁ ବ୍ୟବହାର କରିବା କଷ୍ଟକର କରିଥାଏ | |

ସଂଖ୍ୟା କିମ୍ବା ପ୍ରତୀକ ସହିତ ଅକ୍ଷର ମଧ୍ଯ ବ୍ୟବହାର କରି। 2। ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ମୁଖ୍ୟ ପ୍ରସ୍ତୁତି ପଦ୍ଧତିଗୁଡ଼ିକର ତୁଳନା |

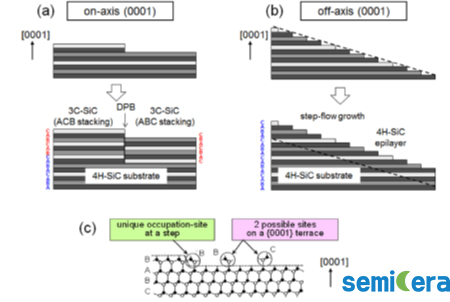

ଏକ ନିର୍ଦ୍ଦିଷ୍ଟ ଟିଲ୍ଟ ଆଙ୍ଗଲ୍ ସହିତ ଅଫ୍-ଅକ୍ଷରେ {0001} ସବଷ୍ଟ୍ରେଟ୍ ଉପରେ, ଚିତ୍ର 2 (ଖ) ରେ ଦେଖାଯାଇଥିବା ପରି, ଷ୍ଟେପ୍ ପୃଷ୍ଠର ଘନତା ବଡ଼, ଏବଂ ଷ୍ଟେପ୍ ପୃଷ୍ଠର ଆକାର ଛୋଟ, ଏବଂ ସ୍ଫଟିକ୍ ନ୍ୟୁକ୍ଲିୟେସନ୍ ସହଜ ନୁହେଁ | ଷ୍ଟେପ୍ ପୃଷ୍ଠରେ ଘଟେ, କିନ୍ତୁ ପ୍ରାୟତ the ପଦକ୍ଷେପର ମିଶ୍ରଣ ସ୍ଥାନରେ ଘଟିଥାଏ | ଏହି କ୍ଷେତ୍ରରେ, କେବଳ ଗୋଟିଏ ନ୍ୟୁକ୍ଲିଏଟିଙ୍ଗ୍ ଚାବି ଅଛି | ତେଣୁ, ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତର ସବଷ୍ଟ୍ରେଟ୍ ର ଷ୍ଟାକିଂ କ୍ରମକୁ ସଂପୂର୍ଣ୍ଣ ରୂପେ ନକଲ କରିପାରିବ, ଯାହାଦ୍ୱାରା ବହୁ-ପ୍ରକାରର ସହଭାଗିତା ସମସ୍ୟା ଦୂର ହେବ |

ସଂଖ୍ୟା କିମ୍ବା ପ୍ରତୀକ ସହିତ ଅକ୍ଷର ମଧ୍ଯ ବ୍ୟବହାର କରି। 3। 4H-SiC ଷ୍ଟେପ୍ କଣ୍ଟ୍ରୋଲ୍ ଏପିଟାକ୍ସି ପଦ୍ଧତିର ଶାରୀରିକ ପ୍ରକ୍ରିୟା ଚିତ୍ର |

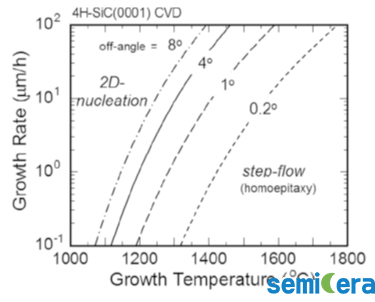

ସଂଖ୍ୟା କିମ୍ବା ପ୍ରତୀକ ସହିତ ଅକ୍ଷର ମଧ୍ଯ ବ୍ୟବହାର କରି। 4H-SiC ଷ୍ଟେପ୍-ନିୟନ୍ତ୍ରିତ ଏପିଟାକ୍ସି ପଦ୍ଧତି ଦ୍ C ାରା CVD ଅଭିବୃଦ୍ଧି ପାଇଁ ଗୁରୁତର ଅବସ୍ଥା |

ସଂଖ୍ୟା କିମ୍ବା ପ୍ରତୀକ ସହିତ ଅକ୍ଷର ମଧ୍ଯ ବ୍ୟବହାର କରି। 5। 4H-SiC ଏପିଟାକ୍ସିରେ ବିଭିନ୍ନ ସିଲିକନ୍ ଉତ୍ସ ଅନ୍ତର୍ଗତ ଅଭିବୃଦ୍ଧି ହାରର ତୁଳନା |

ବର୍ତ୍ତମାନ, ନିମ୍ନ ଏବଂ ମଧ୍ୟମ ଭୋଲଟେଜ୍ ପ୍ରୟୋଗଗୁଡ଼ିକରେ ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏପିଟାକ୍ସି ଟେକ୍ନୋଲୋଜି ଅପେକ୍ଷାକୃତ ପରିପକ୍ୱ ଅଟେ (ଯେପରିକି 1200 ଭୋଲ୍ଟ ଉପକରଣ) | ମୋଟା ସମାନତା, ଡୋପିଂ ଏକାଗ୍ରତା ସମାନତା ଏବଂ ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ତ୍ରୁଟି ବଣ୍ଟନ ଏକ ଅପେକ୍ଷାକୃତ ଭଲ ସ୍ତରରେ ପହଞ୍ଚିପାରେ, ଯାହା ମ middle ଳିକ ଏବଂ ନିମ୍ନ ଭୋଲଟେଜ୍ SBD (ସ୍କଟ୍କି ଡାୟୋଡ୍), MOS (ଧାତୁ ଅକ୍ସାଇଡ୍ ସେମିକଣ୍ଡକ୍ଟର ଫିଲ୍ଡ ଇଫେକ୍ଟ ଟ୍ରାନଜିଷ୍ଟର) ର ଆବଶ୍ୟକତାକୁ ପୂରଣ କରିପାରିବ | ଜଙ୍କସନ ଡାୟୋଡ୍) ଏବଂ ଅନ୍ୟାନ୍ୟ ଉପକରଣଗୁଡ଼ିକ |

ତଥାପି, ଉଚ୍ଚ ଚାପ କ୍ଷେତ୍ରରେ, ଏପିଟାକ୍ସିଆଲ୍ ୱାଫର୍ ଅନେକ ଚ୍ୟାଲେଞ୍ଜକୁ ଦୂର କରିବାକୁ ପଡିବ | ଉଦାହରଣ ସ୍ .ରୁପ, 10,000 ଭୋଲ୍ଟକୁ ପ୍ରତିରୋଧ କରିବାକୁ ଥିବା ଉପକରଣଗୁଡ଼ିକ ପାଇଁ, ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଘନତା ପ୍ରାୟ 100μm ହେବା ଆବଶ୍ୟକ | ଲୋ-ଭୋଲଟେଜ୍ ଉପକରଣଗୁଡ଼ିକ ତୁଳନାରେ, ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରର ଘନତା ଏବଂ ଡୋପିଂ ଏକାଗ୍ରତାର ସମାନତା ବହୁତ ଭିନ୍ନ, ବିଶେଷତ the ଡୋପିଂ ଏକାଗ୍ରତାର ସମାନତା | ସେହି ସମୟରେ, ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରରେ ଥିବା ତ୍ରିରଙ୍ଗା ତ୍ରୁଟି ମଧ୍ୟ ଉପକରଣର ସାମଗ୍ରିକ କାର୍ଯ୍ୟଦକ୍ଷତାକୁ ନଷ୍ଟ କରିଦେବ | ହାଇ-ଭୋଲଟେଜ୍ ପ୍ରୟୋଗଗୁଡ଼ିକରେ, ଡିଭାଇସ୍ ପ୍ରକାରଗୁଡିକ ଦ୍ୱିପାକ୍ଷିକ ଉପକରଣ ବ୍ୟବହାର କରିବାକୁ ପ୍ରବୃତ୍ତି କରନ୍ତି, ଯାହାକି ଏପିଟାକ୍ସିଆଲ୍ ସ୍ତରରେ ଏକ ଉଚ୍ଚ ସଂଖ୍ୟାଲଘୁ ଜୀବନକାଳ ଆବଶ୍ୟକ କରେ, ତେଣୁ ସଂଖ୍ୟାଲଘୁଙ୍କ ଜୀବନକାଳରେ ଉନ୍ନତି ଆଣିବା ପାଇଁ ପ୍ରକ୍ରିୟା ଅପ୍ଟିମାଇଜ୍ ହେବା ଆବଶ୍ୟକ |

ବର୍ତ୍ତମାନ, ଘରୋଇ ଏପିଟାକ୍ସି ମୁଖ୍ୟତ 4 4 ଇଞ୍ଚ ଏବଂ 6 ଇଞ୍ଚ ଅଟେ ଏବଂ ବଡ଼ ଆକାରର ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏପିଟାକ୍ସିର ଅନୁପାତ ବର୍ଷକୁ ବର୍ଷ ବୃଦ୍ଧି ପାଉଛି | ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏପିଟାକ୍ସିଆଲ୍ ସିଟ୍ ର ଆକାର ମୁଖ୍ୟତ sil ସିଲିକନ୍ କାର୍ବାଇଡ୍ ସବଷ୍ଟ୍ରେଟ୍ ର ଆକାର ଦ୍ୱାରା ସୀମିତ | ବର୍ତ୍ତମାନ, 6-ଇଞ୍ଚର ସିଲିକନ୍ କାର୍ବାଇଡ୍ ସବଷ୍ଟ୍ରେଟ୍ ବ୍ୟବସାୟିକ ହୋଇଛି, ତେଣୁ ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏପିଟାକ୍ସିଆଲ୍ ଧୀରେ ଧୀରେ 4 ଇଞ୍ଚରୁ 6 ଇଞ୍ଚକୁ ଗତି କରୁଛି | ସିଲିକନ୍ କାର୍ବାଇଡ୍ ସବଷ୍ଟ୍ରେଟ୍ ପ୍ରସ୍ତୁତି ପ୍ରଯୁକ୍ତିବିଦ୍ୟା ଏବଂ କ୍ଷମତାର ବିସ୍ତାର ସହିତ କ୍ରମାଗତ ଉନ୍ନତି ସହିତ ସିଲିକନ୍ କାର୍ବାଇଡ୍ ସବଷ୍ଟ୍ରେଟର ମୂଲ୍ୟ ଧୀରେ ଧୀରେ ହ୍ରାସ ପାଉଛି | ଏପିଟାକ୍ସିଆଲ୍ ସିଟ୍ ମୂଲ୍ୟର ରଚନାରେ ସବଷ୍ଟ୍ରେଟ୍ ମୂଲ୍ୟର 50% ରୁ ଅଧିକ ଅଟେ, ତେଣୁ ସବଷ୍ଟ୍ରେଟ୍ ମୂଲ୍ୟ ହ୍ରାସ ହେବା ସହିତ ସିଲିକନ୍ କାର୍ବାଇଡ୍ ଏପିଟାକ୍ସିଆଲ୍ ସିଟ୍ ମୂଲ୍ୟ ମଧ୍ୟ ହ୍ରାସ ପାଇବ ବୋଲି ଆଶା କରାଯାଉଛି |

ପୋଷ୍ଟ ସମୟ: ଜୁନ୍ -03-2024 |